İSMED Şeker Fabrikası Projesi ( FPGA ile yapıldı )

2019 Yılının Aralık ayında bitirdiğim proje FPGA ile tamamlanmıştır. Bu proje amacı fabrikadaki şekerlerin paketlenmesi için kullanılmıştır.

Şekil 1: Çalışma grafiği

Şekil1 de görüldüğü gibi start veriliğinde motor hareketi ile palet hareket edecek ve servo motor kol yardımı ile kutuları palete itecektir. palet yolunda bulunan proximity sensor ile kutu içinde ne kadar malzeme olmasını sayarak belirleyecektir. ( bu örnekte 3 şeker paketi olarak belirlendi ) Belirlenen sayı adedi kadar palet yardımı ile kutuya atıldığında başlangıç durumuna gelecektir

b1 : sayıcı proximity

b2 : servo motorunun palete atacağı şekerin o durumda olup olamaması durumunu gosteren proximity

Şekil 2 : Servo motorun çalışması için Pulse genişliği

Servo motor 20ms ( 50hz ) periyodunda çalışır. Bu 20ms periyotta 1 ms genişliğinde pulse uygulanırsa 0 derece , 1.5 ms için 90 derece , 2ms için ise 180 derece hareket eder. Bu bilgiyi FPGA programlarken kullanacağız.

•Servo Motor Dönüş Hızı

Biz programımızı servo motorun bir tam devrini 5 ms'de tamamlayacak şekilde ayarladık. Programımızda

Motor hız(s) = ((dcycle_max- dcycle_min)*period) / duty_in denklemini kullanırsak,

Duty_in= ((150000-50000)*20 ms)/5 s= 400 olarak hesaplarız.

Biz programımızı servo motorun bir tam devrini 5 ms'de tamamlayacak şekilde ayarladık. Programımızda

Motor hız(s) = ((dcycle_max- dcycle_min)*period) / duty_in denklemini kullanırsak,

Duty_in= ((150000-50000)*20 ms)/5 s= 400 olarak hesaplarız.

•Kontrol sinyalimizin Duty Cycle'ı 1ms ile 3ms olması gerekecek. Bundan dolayı programımızda dcycle_max ile dcycle_min adında iki

sabit tanımlayacağız

•dcycle_max=Pulse

genişliğimizin alacağı maksimum değeri gösterecek.

(3ms/clock period=3 ms/ 20 ns=150000)

(3ms/clock period=3 ms/ 20 ns=150000)

•dcycle_min=Pulse

genişliğimizin alacağı minimum değeri gösterecek.

(1ms/clock period=1 ms/ 20 ns=50000)

(1ms/clock period=1 ms/ 20 ns=50000)

Duty Cycle : Görev döngüsü Elektronikte sistemin aktif olduğu zaman süresinin toplam süreye olan oranıdır.

Şekil 3 Similasyon

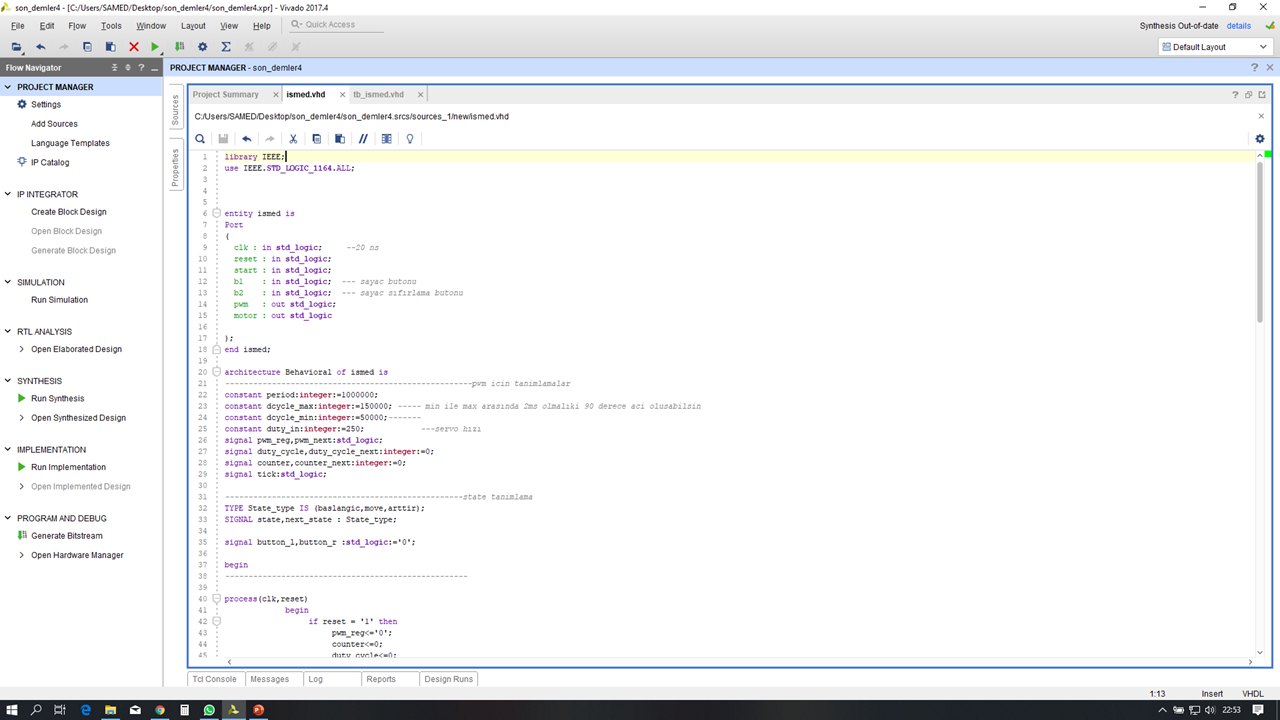

VHDL Kodu :

VHDL Test Kodu :

Yorumlar

Yorum Gönder